Семейство высокопроизводительных цифровых сигнальных процессоров TDA755X предназначено для решения задач в области распознавания и синтеза реци, подавления эха и шумов.

Отметим особенности сигнальных процессоров семейства TDA755X

- 24-битное вычислительное ядро;

- большой объем интегрированной памяти (до 16 Кслов ПЗУ/ОЗУ и до 16 Кслов ОЗУ);

- встроенные 2 канальные ЦАП и АЦП с разрядностью 16 Бит;

- управляемая частота дискретизации от 4 до 48 кГц;

- встроенный контроллер дополнительной памяти с поддержкой флэш памяти, статического и динамиче ского ОЗУ;

- последовательный интерфейс, работающий в режи мах I2C или SPI.

Блок схема микросхем приведена на рис 1, назначение выводов — в табл. 1, а цоколевка — на рис 2.

Рис. 1

Блок-схема микросхем

Рис. 2

Цоколевка микросхем

Микросхемы включают в себя три основных модуля 24-битный цифровой сигнальный процессор (ЦСП), па мять (ПЗУ и ОЗУ) и периферийные устройства.

Параметры и функции процессорного ядра:

- тактовая частота 50 МГц;

- операции сложения и умножения выполняются за один такт;

- два 56 битных аккумулятора;

- 48 битные или параллельные 24-битные команды загрузки регистров;

- 64 вектора прерываний;

- возможность программного запрещения и маскиро вания прерываний;

- команды организации циклов;

- три шины данных;

- три шины адреса.

Интегрированная память включает в себя 16384 24 битных слова ПЗУ и такой же объем ОЗУ В состав периферийных устройств входят последовательный аудиоинтерфейс, интерфейс I2C/SPI, интерфейс внешней памяти, тактовый генератор, кодек (кодер/декодер).

Таблица 1

| № вывода | Обозначение | Категория сигнала | Краткое описание |

| 1-2 | EMI_AD5 | вход/выход | Мультиплексная шина адреса/данных интерфейса внешней памяти |

| 3 | VDD | вход | Напряжение питания цифровой части микросхемы |

| 4 | GND | вход | Общий провод питания |

| 5 | EMI_AD7 | вход/выход | Сигнал мультиплексной шины адреса/данных интерфейса внешней памяти |

| 06-13 | EMI_A8/A15 | выход | Шина адреса интерфейса внешней памяти |

| 14 | VDD | вход | Напряжение питания цифровой части микросхемы |

| 15 | GND | вход | Общий провод питания |

| 16-21 | EMI_A16/A21 | выход | Шина адреса интерфейса внешней памяти |

| 22 | DWRN | выход | Сигнал «запись» интерфейса внешней памяти |

| 23 | TEST1 | вход | Тестовый вход № 1 (активный уровень — высокий) |

| 24 | TEST2 | вход | Тестовый вход № 2 (активный уровень — низкий) |

| 25 | MISO | вход/выход | Выход данных в режиме SPI Master, вход данных в режиме SPI Slave |

| 26 | MOSI | вход/выход | Вход данных в режиме SPI Master, выход данных в режиме SPI Slave |

| 27 | VDD | вход | Напряжение питания цифровой части микросхемы |

| 28 | GND | вход | Общий |

| 29 | TEST3 | вход | Тестовый вход № 3 (активный уровень - высокий) |

| 30 | SDI | вход | Данные последовательного аудиоинтерфейса |

| 31 | SCK | вход/выход | Тактовый сигнал последовательного аудиоинтерфейса |

| 32 | LRCK | вход/выход | Управляющий тактовый сигнал (правый/левый канал) последовательного аудиоинтерфейса |

| 33 | VDD | вход | Напряжение питания цифровой части |

| 34 | GND | вход | Общий |

| 35 | SDO | выход | Выход данных последовательного аудиоинтерфейса |

| 36 | GPIO1 | вход/выход | Программируемый порт ввода/вывода |

| 37 | GPIOO | вход/выход | — «— |

| 38 | GPIO5 | вход/выход | — «— |

| 39 | DBCK | вход/выход | Тактовый сигнал отладочного порта/сигнал состояния № 1 Может быть использован как сигнал GPIO9 |

| 40 | DBIN | вход/выход | Вход данных отладочного порта/сигнал состояния № 0 Может быть использован как сигнал GPIO11 |

| 41 | DBOUT | вход/выход | Выход последовательных данных отладочного порта Может быть использован как сигнал GPIO10 |

| 42 | DBRQN | вход | Сигнал запроса режима отладки |

| 43 | NRESET | вход | Общий сброс микросхемы Активный уровень — низкий |

| 44 | INTN | вход | Сигнал внешнего прерывания Активный уровень — низкий |

| 45 | SCL/SCK | вход/выход вход/выход | Тактовый сигнал интерфейса I2С В режиме интерфейса SPI - тактовый сигнал шины SPI |

| 46 | SDA/SS | вход/выход вход | Данные интерфейса I2C В режиме последовательного интерфейса SPI — сигнал выбора подчиненного устройства | 47 | VDD | вход | Напряжение питания цифровой части |

| 48 | GND | вход | Общий |

| 49 | GPIO2 | вход/выход | Программируемый порт ввода/вывода |

| 50 | GPIO6 | вход/выход | -«- |

| 51 | GPIO3 | вход/выход | — « — |

| 52 | CGND | вход | Общий |

| 53 | CVDD | вход | Напряжение питания модуля кодека |

| 54 | VOUTR | выход | Аналоговый сигнал с ЦАП (правый канал) |

| 55 | VOUTL | выход | Аналоговый сигнал с ЦАП (левый канал) |

| 56 | VDD | вход | Напряжение питания цифровой части |

| 57 | GND | вход | Общий |

| 58 | VINR | вход | Аналоговый сигнал для АЦП (правый канал) |

| 59 | VINL | вход | Аналоговый сигнал для АЦП (левый канал) |

| 60 | CGNDA | вход | Общий |

| 61 | TEST4 | выход | Соединен с согласующим резистором 22 кОм |

| 62 | CVDDA | вход | Напряжение питания модуля кодека |

| 63 | VREF | выход | Опорное напряжение от модуля кодека |

| 64 | REFCAP | выход | Шунтирующий конденсатор выхода опорного напряжения |

| 65 | GPIO7 | вход/выход | Программируемый порт ввода/вывода |

| 66 | GPIO4 | вход/выход | — «— |

| 67 | VDD | вход | Напряжение питания цифровой части |

| 68 | CLKOUT | выход | Тактовый сигнал с делителя частоты |

| 69 | XTI | вход | Подключение кварцевого резонатора |

| 70 | PGND | вход | Общий |

| 71 | PVCC | вход | Питающее напряжение тактового генератора |

| 72 | XTO | выход | Подключение кварцевого резонатора |

| 73 | ALE | выход | Подтверждение адреса на шине интерфейса внешней памяти (активный уровень — высокий) |

| 74 | GND | вход | Общий |

| 75 | DRDN | выход | Сигнал «чтение» интерфейса внешней памяти |

| 76-80 | EMI_AD0/AD4 | вход/выход | Сигнал мультиплексной шины адреса/данных интерфейса внешней памяти |

Последовательный аудиоинтерфейс передает цифровой звуковой сигнал от внешнего источника к ЦСП микросхемы, а также цифровые данные от ЦСП к внешнему ЦАП.

Интерфейсы I2C/SPI соединяют микросхемы с другим оборудованием, совместимым с этими интерфейсами.

Интерфейс внешней памяти позволяет обращаться к дополнительным банкам памяти, установленным вне микросхемы. Поддерживаются динамическая оперативная память (DRAM), статическая оперативная память (SRAM) и энергонезависимая память (FLASH).

Параметры и функции внешнего интерфейса памяти:

- 4 битная шина данных для динамического ОЗУ (DRAM) и 8 битная для статического ОЗУ (SRAM);

- 22-битная шина адреса мультиплексирована с 8-битной шиной данных;

- возможность обращения к байту, 16 битному слову и 24-битному слову при работе со статическим и дина мическим ОЗУ;

- адресуемая память при работе с динамическим ОЗУ до 256 Мбит;

- 4 Мбайта адресуемого статического ОЗУ.

Тактовый генератор микросхемы выполняет генерацию следующих тактовых сигналов:

- DCLK - тактовый сигнал для ЦСП;

- MCLK — опорный сигнал для кодека;

- LRCLK — тактовый сигнал для правого/левого каналов последовательного аудиоинтерфейса и кодека;

- сигнал тактирования сдвига для последовательного аудиоинтерфейса и кодека.

Параметры и функции кодека:

- аналого-цифровое дельта-сигма преобразование входного стереосигнала;

- динамический диапазон АЦП - 80 дБ;

- цифро-аналоговое дельта-сигма преобразование выходного цифрового стереосигнала;

- частота дискретизации от 4 до 48 кГц;

- цифровый вход и выход через последовательный аудиоинтерфейс.

Функциональные возможности микросхем приведе ны в табл 2.

Таблица 2

| Обознач. | Тип памяти для программ | Основная функция | Режим послед. интерф-са | Внеш. память | Аудио вход | Аудио выход | Програм. обеспеч. |

| TDA7550R | ОЗУ | На выбор | Master или Slave I2C | FLASH или RAM | Есть (опред. примен-ем) | Есть (опред. примен-ем) | Опред. примен-ем |

| TDA7550 | ПЗУ | Распознавание речи | Slave I2C | FLASH | Есть (голосовой сигнал) | Есть (голосовой сигнал) | ASR 311 Lernout& Hauspie |

| TDA7551 | - | Голосовая идентификация | Slave I2C | FLASH | Есть (голосовой сигнал) | Есть (голосовой сигнал) | SV208 Lernout& Hauspie |

| TDA7552 | - | Синтезатор речи | Slave I2C | - | Нет | TTS3000 Lernout& Hauspie | |

| TDA7553 | - | Цифровая фильтрация сигнала | Master I2C или SPI | (RAM) | Есть (необраб. сигнал) | Есть (обработ. сигнал) | Программа обработки NCTI |

Микросхема TDA7550 с программным обеспечением ASR311 позволяет реализовать систему распознавания речи Параметры и функции такой системы:

- качественное распознавание слов из базового набора в широком диапазоне изменений параметров голоса;;

- высокая помехозащищенность алгоритма распознавания;

- запоминание новых слов в дополнение к базовому набору;

- возможность записывать во внешнюю FLASH-память голосовые сообщения для поддержки голосового ин терфейса;

- управление всеми функциями системы осуществляется через интерфейс I2C;

- доступны базовые наборы слов для большинства распространенных языков;

- внешняя FLASH-память используется для хранения базового набора слов (4 Кбайта на одно слово), дополнительного набора слов (4 Кбайт/слово) и голосовых сообщений (11 Кбайт/сек, частота дискретизации 11025 Гц).

Блок схема системы распознавания речи приведена на рис 3.

Рис. 3

Блок схема системы распознавания речи

Микросхема TDA7551 представляет собой однокор пусное решение для систем идентификации голоса с использованием программного обеспечения SV208 Парольные фразы запоминаются при тройном повторении (длительность фразы - 1 2 с) В дальнейшем произнесенная парольная фраза сравнивается с параметрами хранящихся в энергонезависимой памяти парольных фраз Управление системой функциями микросхемы осуществляется через последовательный интерфейс I2C.

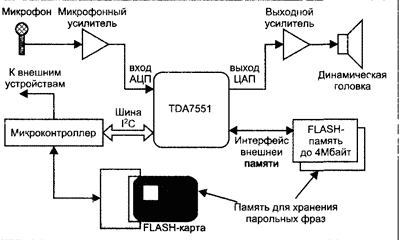

Блок-схема системы идентификации голоса приведена на рис 4.

Рис. 4

Блок схема системы идентификации голоса

Микросхема TDA7552 предназначена для применения в составе системы синтеза речи по схеме «текст-голос». Для построения такой системы кроме ЦСП TDA7552 требуется микроконтроллер ST1O для анализа и преобразования входных текстовых строк.

Блок-схема системы синтеза речи представлена на рис. 5.

Рис. 5

Блок схема системы синтеза речи

Внешнее устройство посылает микроконтроллеру текстовые строки в виде потока символов в кодировке ASCII. Микроконтроллер анализирует и преобразует поступающие данных с учетом используемого языка (информация о преобразовании для различных языков содержится во внешней FLASH-памяти, к которой имеет доступ микроконтроллер). Преобразованные данные микроконтроллер направляет по шине I2C к микросхеме TDA7552, которая преобразует полученные данные в ре чевой сигнал. Программное обеспечение сигнального процессора TDA7552 не зависит от языка входного текста и не требует дополнительной внешней памяти.