ЖК телевизоры с каждым днем завоевывают все большую долю рынка, постепенно вытесняя кинескопные телевизоры. И одно из главных действующих лиц на рынке ЖК телевизоров - компания PHILIPS. Сегодняшняя тема разговора - схемотехника ЖК телевизоров с диагональю экрана 15 дюймов, в частности, ТВ шасси LCD1.15, на котором выпускаются такие телевизоры. Несмотря на небольшие габариты, телевизоры на этом шасси довольно хорошо функционально оснащены. За счет чего? Об этом и пойдет речь в статье.

Технические характеристики и конструкция

На рассматриваемом ТВ шасси выпускаются две модели - "Philips 15PF9925/12S" и "Philips 15PF9925/19S". Основные технические характеристики телевизоров приведены в табл. 1.

Таблица 1. Основные технические характеристики телевизоров "Philips 15PF9925/12S/19S"

Характеристика | Описание |

Системы цветности | PAL/SECAM-B/G, PAL/SECAM-D/К, PAL-I, SECAM L/L1, NTSC-3.58/4.43 (c НЧ входа) |

Тюнер | Цифровой, настройка синтезом частоты (несимметричный вход 50 Ом) |

Каналы | VHF/UHF, CATV/ HYPER |

Тип/диагональ/формат ЖК панели/физическое разрешение | Цветная Активная Матрица LCD XGA TFT /15 дюймов/1024х768 пикселов |

Углы обзора панели | По вертикали - 120°, по горизонтали - 140° |

Яркость | 400 Кд/м2 |

Контрастность | 300:1 |

Стандарты звука | Все аналоговые FM (поднесущие 5,5-5,85 МГц), 2CS B/G, 2CS D/K, NICAM B/G, NICAM D/K |

Интерфейсы | AV-IN, S- VIDEO, PHONE JACK, DTV-IN, DVD-IN, DVD-AUDIO IN, PC AUDIO-IN, PC-IN (D-SUB15PIN), DVI-OUT |

Питание AC/DC-адаптера | Переменное напряжение 95...264 В частотой 50/60 Гц |

Выход AC/DC-адаптера | 12 В, 3 А |

Энергопотребление в рабочем/дежурном режимах | 50/3 Вт |

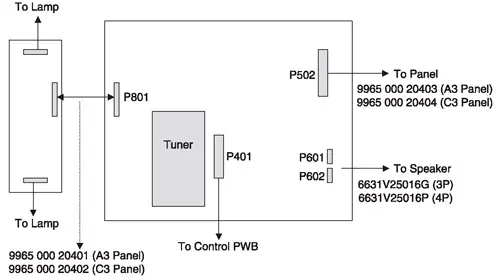

Телевизоры выполнены в пластмассовом корпусе с подставкой, внутри которого находятся ЖК панель, главная плата, плата передней панели, плата DC/AC-конвертора для питания ламп подсветки и динамические головки (см.схему соединений на рис. 1).

Рис. 1. Схема соединений плат

Структурная схема

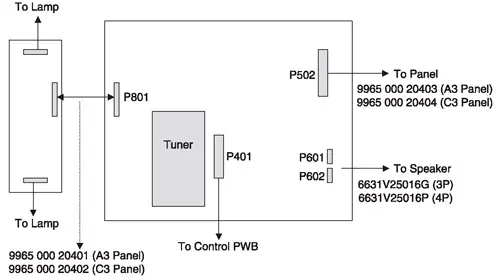

Структурная схема телевизоров приведена на рис. 2. В схеме используется цифровой тюнер с синтезатором частот, радиоканал входит в состав тюнера. На выходах тюнера формируется полный цветовой телевизионный сигнал (ПЦТС), звуковой сигнал 2-ой ПЧ звука и АМ звуковой сигнал.

Рис. 2. Структурная схема шасси LCD1.15E

Видеотракт реализован на многофункциональной микросхеме фирмы Micronas VPC3230D - однокристальном видеопроцессоре, работающем с форматами изображения 4:3 и 16:9. Микросхема может работать в режимах чересстрочной и прогрессивной разверток, имеет входы для подключения внешних композитных ПЦТС, раздельных сигналов RGB, компонентных сигналов CrCb, мультисистемный декодер цветности и другие возможности (см. описание принципиальной схемы). Микросхема управляется по цифровому интерфейсу I2C.

Обработка звукового сигнала на рассматриваемом шасси выполняется цифровым звуковым процессором фирмы MICRONAS MSP3410D. Микросхема работает с аналоговыми звуковыми сигналами всех мировых стандартов и с цифровыми сигналами стандартов NICAM. Она имеет входы для подключения внешних звуковых моно-и стереосигналов. Как и в предыдущем случае, для управления микросхемой служит интерфейс I2C. Кроме того, MSP3410D поддерживает цифровой интерфейс передачи звуковых данных I2S (два входа - один выход, на этом шасси интерфейс не используется).

В качестве графического процессора и интерфейса ЖК панели на этом шасси используется микросхема фирмы MACRONIX MX88L284. Это специализированная микросхема предназначена для управления 8-битными цветными TFT LCD-панелями. В состав микросхемы входят схема масштабирования, генератор экранного меню, интерфейсы (входной, выходной - TMDS, управления внешним ОЗУ типа SDRAM и связи с управляющим микроконтроллером). На входы микросхемы поступают аналоговые видеосигналы RGB с видеопроцессора и цифровые (8-битный код) с АЦП AD9884 (преобразует аналоговые видеосигналы RGB с разъема D-Sub, к которому может быть подключен компьютер). На выходе микросхемы формируются 8-битный 21разрядный код видеосигнала и тактовые сигналы.

В качестве главного микроконтроллера на этом шасси используется микросхема фирмы INFINEON серии SDA55XX. С тюнером, видеопроцессором, звуковым процессором и АЦП контроллер связан по интерфейсу I2C, а с графическим контроллером - по отдельной 3-проводной шине MX-CS, МХ-DA, МХ-CK. Кроме того, SDA55XX поддерживает пользовательский интерфейс - кнопки передней панели и ИК порт системы ДУ.

Перейдем к рассмотрению особенностей принципиальной электрической схемы.

Принципиальная электрическая схема

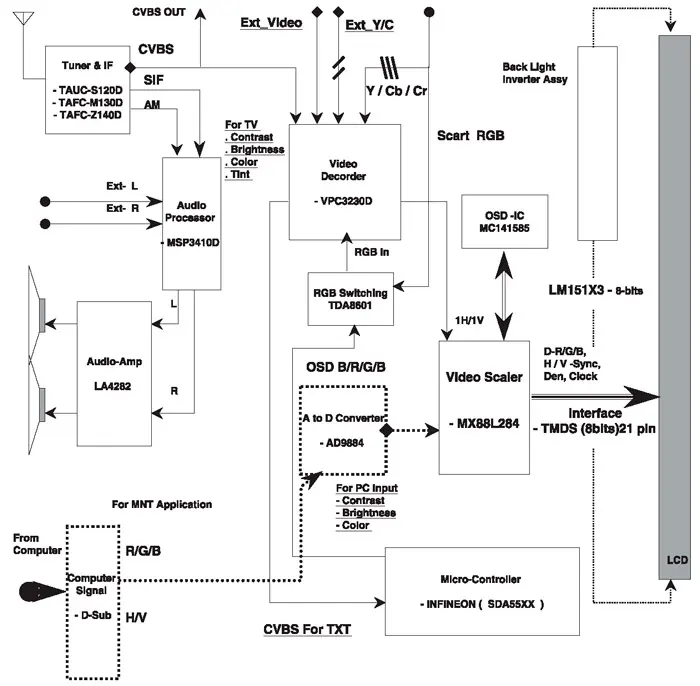

Принципиальная электрическая схема телевизоров приведена на рис. 3. (схему можно скачать здесь)

Радиоканал и видеотракт

ВЧ телевизионный сигнал поступает на антенный вход всеволнового тюнера типа TAUC-S120D (аналоги - TAFC-M130D, TAFC-Z140D) (рис. 1 и 2). В составе тюнера имеются встроенный тракт ПЧ и цифровой синтезатор частоты. Тюнер подключен к главной плате через переходную плату и 10-контактные соединители Р102В и Р103В. Тюнером управляет микроконтроллер IC101 по цифровой шине I2C. Сигналы управления SCL и SDA с выв. 3, 4 IC101 через шинные формирователи на полевых транзисторах Q1 и Q2(согласова-ние уровней 3 В и 5 В) поступают на выв. 4 и 5 тюнера TU101.

На выходе тракта ПЧ тюнера формируется полный цветовой телевизионный сигнал (ПЦТС) (контакт 8 Р102В), сигнал 2-й ПЧ звука (контакт 6 Р102В) и звуковой сигнал (контакт 4 Р102В).

Для питания аналоговой и цифровой частей схемы тюнера на него (контакт 7 Р103В) поступает напряжение 5 В от стабилизатора IC803. Кроме того, для формирования напряжения настройки на выв. 9 тюнера поступает напряжение 33 В от стабилизатора D103, который питается от конвертера IC904 (см. описание схемы питания).

ПЦТС снимается с выхода тюнера и через эмиттерный повторитель на транзисторе Q102 поступает на один из аналоговых входов видеопроцессора - выв. 74 IC301 (рис. 3). На другие входы (выв. 7173, 75) поступают внешние видеосигналы и сигнал цветности с разъемов НЧ входаJ402, J403. Сигнал яркости Y с разъема S-video J403 (контакт 8) подается на выв. 5 IC301.

Если к телевизору подключен источник компонентных сигналов CrCb, то эти сигналы с разъема SCART (контакты 20, 2, 6) через повторители на транзисторахQ402, Q403 подаются на компонентный вход микросхемы IC301 - выв. 4-6.

Микросхема имеет вход для аналоговых сигналов RGB (выв. 1-3). На этот вход подаются RGB-сигналы с коммутатора IC107 (TDA8701), на который подаются RGB-сигналы с микроконтроллера IC101 (выв. 38-40, используется в варианте ТВ с телетекстом) и с разъема SCART J402 (контакты 7, 11, 15). Сигнал вставки внешних RGB-сигналов формируется микроконтроллером (выв. 41). Отсюда он подается на вход коммутатора IC107 (выв. 14), а с его выхода (выв. 13) - на видеопроцессор IC301 (выв. 79).

В состав видеопроцессора VPC3220D входят следующие узлы:

- АЦП со схемами привязки уровня черного и АРУ на входе;

- быстродействующий адаптивный цифровой фильтр (селектор) сигналов яркости и цветности систем PAL/NTSC;

- мультистандартный декодер цветности PAL/NTSC/SECAM;

- 4 входа для аналоговых ПЦТС;

- два входа для аналоговых сигналов RGB/YCrCb;

- мультистандартный синхропроцессор;

- процессор PAL+;

- PIP-процессор для 4-х размеров изображения (1/4, 1/9, 1/16 и 1/36 от нормального размера) с разрешением 8 бит;

- блок регулировки контрастности, яркости, насыщенности и цветового тона;

- задающий генератор частотой 20,25 МГц;

- интерфейс для внешней памяти;

- декодер интерфейса I2C.

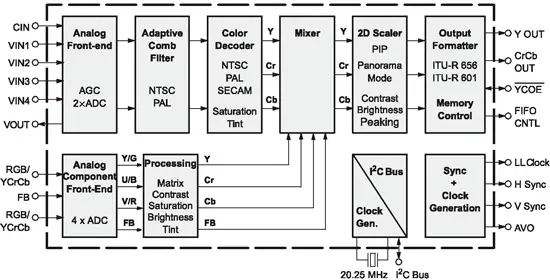

Архитектура микросхемы VPC3220D приведена на рис. 4. Микросхема изготавливается в 80-выводном корпусе PQFP, питается напряжением 3,3 В и потребляет в рабочем режиме примерно 170...180 мА, а в дежурном - до 1 мА. На этом шасси микросхема питается (выв. 10, 29, 36, 45, 52) от понижающего DC/DC-конвертора на микросхеме IC804 типа SI786.

Рис. 4. Архитектура видеопроцессора VPC3220

На выходе видеопроцессора, в зависимости от выбранного режима, формируются цифровые 8битные коды компонентных сигналов яркости (31-34, 37-40), цветности (выв. 41-44, 47) и синхронизации (выв. 27, 28, 53, 54, 56, 57). При этом микросхема поддерживает различные форматы выходных сигналов: DIGIT3000 (4:2:2 YCrCb, частота дискретизации 20,25 МГц), ортогональные (4:2:2 и 4:1:1) и ITU R656 (4:2:2, частота синхронизации 13,5 МГц). Эти сигналы поступают на вход графического контроллераIC501: выв. 310 - сигнал Y выв. 21-28 - сигнал Sync и выв. 12-19 - сигнал CrCb.

Микросхема IC501 типа MX88L284 фирмы MACRONIX представляет собой графический контроллер ЖК панелей, имеющих физическое разрешение от VGA (640x480) до SXGA (1280x1024).

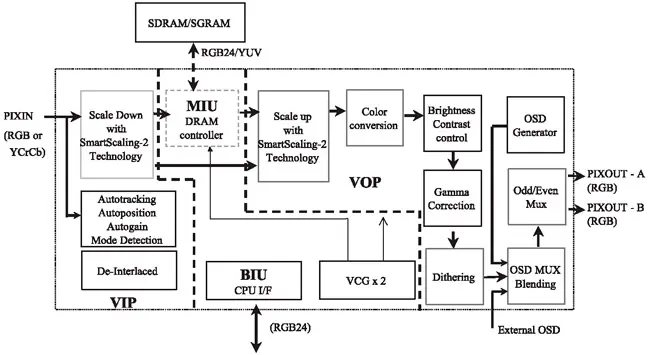

Его архитектура (см. рис. 5) включает в себя четыре основных блока: входной видеопроцессор VIP (Video Input Processor), интерфейс памяти MIU (Memory Interface Unit), выходной видеопроцессор VOP (Video Output Processor) и интерфейс шины процессора BIU (CPU Bus Interface Unit).

Рис. 5. Архитектура графического контроллера MX88L284

Входной видеопроцессор VIP принимает цифровые данные от видеодекодера, в нашем случае - от видеопроцессора IC301 или от АЦП IC201 (от видеокарты персонального компьютера).

Блок автоподстройки и детектирования режима определяет параметры входного сигнала, в соответствии с которыми происходит его дальнейшая обработка. В зависимости от разрешения сигнал масштабируется по фирменной технологии SmartScaling-2 Technology в одном из блоков - Scaler Down или Scaler Up. В качестве буфера для хранения строк масштабируемого изображения используется внешняя память типа SDRAM IC502 и IC503 (K4S161622D). Это микросхемы фирмы SAMSUNG объемом 16 Мбайт со структурой 512 кбайт х 16 разрядов х 2 банка.

Выходной видеопроцессор VOP считывает данные из буфера строк и формирует из них в буфере полей данные для отображения на ЖК панели. В составе этого блока есть узлы регулировки яркости, контрастности и гамма-коррекции изображения. Несмотря на наличие в составе IC501 генератора OSD, экранное меню формируется внешним генератором IC505 (SC786107DWR2). Команды и данные для него формируются микроконтроллером IC101 и по интерфейсу I2C поступают на микросхему IC505 (выв. 7, 8).

Окончание следует...

Автор: Павел Потапов (г. Москва)

Источник: Ремонт и сервис